Some of the commentary in response to Part 1 on this topic suggested that the two 1 pF capacitors, C4 and C5, had to be put in series for lack of availability of 0.5 pF parts.

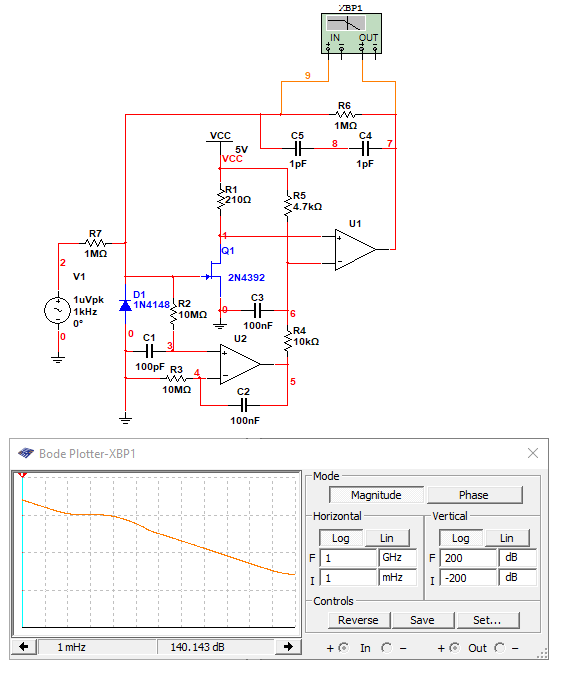

A simulation of that presented circuit is seen as follows:

Part selections differ somewhat from the original. These op-amps are virtual, the JFET is merely an available part from the simulation software and the diode represents the original photodiode. For all of that, these are all close enough. Please note the Bode plot of this configuration.

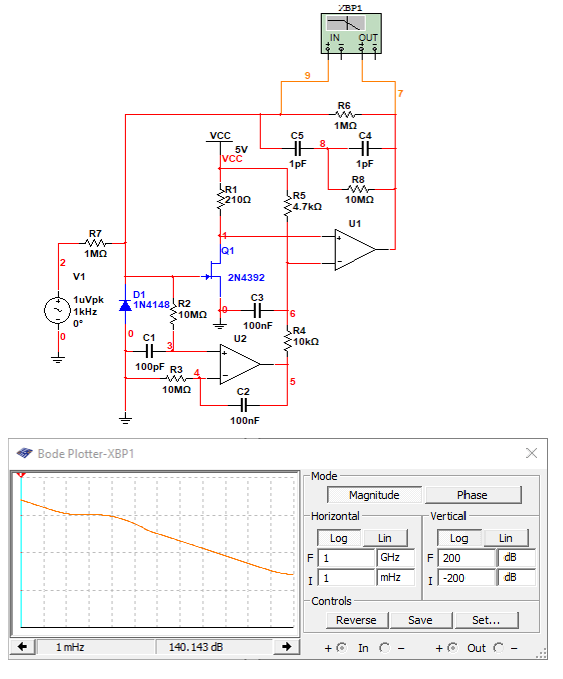

To keep using the pair of 1 pF capacitors, the following schematic is the same as above but with the addition of one more resistor, R8, in parallel with C4

Figure 2 The circuit without a floating node (an additional resistor R8 added in parallel with C4) and its Bode plot simulation.

At 10 MΩ, resistor R8 provides a DC path for the formerly floating node to keep that node’s voltage from unpredictably shifting. Note that the Bode plot for this modified circuit is indistinguishable from the plot seen before.

Other options for tethering the formerly floating node exist as well. For example, R8 could be tied from the C4 and C5 junction to ground, again, with no visible effect on the Bode plot.

The best choice is best left to the designer.

John Dunn is an electronics consultant, and a graduate of The Polytechnic Institute of Brooklyn (BSEE) and of New York University (MSEE).

No floating nodes

The schematic below was screen-shot from a LinkedIn group. I heard alarm bells go off in my head when I saw it

Capacitors C4 and C5 are placed in series with each other so that their common node has no DC path to anywhere. When I worked on some spacecraft projects, this was absolutely a forbidden thing to do because any floating node like this could drift to an indeterminately high voltage and lead to voltage breakdown.

Even in an earthly milieu, this can be a problem. Imagine something being used or merely being transported or shipped in a thunderstorm environment. Dr. Frankenstein’s lightning bolts could do some real harm.

I have no idea why in the above schematic the series pair of C4 and C5 wasn’t simply made a single 0.5 pF capacitance.

The basic badness of letting something float has been looked at before in “Design precaution: Leave nothing floating”.

If you need something more than just Online Homework Help, We have a Bouquet of services to Offer .Our expert tutors are available 24/7, to help you get good grades in any way possible.www.eagletutor.in